# 8101/8104 Gigabit Ethernet Controller

# **Technical Manual**

July 2000

Order Number R14017

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

Document DB14-000123-00, First Edition (July 2000) This document describes revision/release 1 of the LSI Logic Corporation 8101/8104 Gigabit Ethernet Controller and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

#### To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 2000 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design is a registered trademark of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

# Preface

This book is the primary reference and technical manual for the 8101/8104 Gigabit Ethernet Controller. It contains a complete functional description and includes complete physical and electrical specifications for the 8101/8104.

The 8104 is functionally the same as the 8101, except that the 8104 is in a 208-pin Ball Grid Array (BGA) package and the 8101 is in a 208-pin Plastic Quad Flat Pack (PQFP) package

#### Audience

This document assumes that you have some familiarity with application specific integrated circuits and related support devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the 8101/8104 Gigabit Ethernet Controller for possible use in a system

- Engineers who are designing the 8101/8104 Gigabit Ethernet Controller into a system

#### Organization

This document has the following chapters:

- Chapter 1, Introduction, describes the 8101/8104 Gigabit Ethernet Controller, its basic features and benifits. This chapter also describes the differences between the 8101 and 8104.

- Chapter 2, Functional Description, provides a high level description of the 8101/8104 Gigabit Ethernet Controller.

- Chapter 3, Signal Descriptions, provides a description of the signals used and generated by the 8101/8104 Gigabit Ethernet Controller.

- Chapter 4, **Registers**, provides a description of the register addresses and definitions.

- Chapter 5, Application Information, provides application considerations.

- Chapter 6, **Specifications**, describes the specifications of the 8101/8104 Gigabit Ethernet Controller.

#### Abbreviations Used in This Manual

| 100BASE-FX<br>100BASE-TX<br>10BASE-T<br>4B5B<br>BGA | 100 Mbit/s Fiber Optic Ethernet<br>100 Mbit/s Twisted-Pair Ethernet<br>10 Mbit/s Twisted-Pair Ethernet<br>4-Bit 5-Bit<br>Ball Grid Array |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| CLK<br>CRC                                          | Clock                                                                                                                                    |

| CRS                                                 | Cyclic Redundancy Check<br>Carrier Sense                                                                                                 |

| CSMA                                                | Carrier Sense Multiple Access                                                                                                            |

| CWRD                                                | Codeword                                                                                                                                 |

| DA                                                  | Destination Address                                                                                                                      |

| ECL                                                 | Emitter-Coupled Logic                                                                                                                    |

| EOF                                                 | End of Frame                                                                                                                             |

| ESD                                                 | End of Stream Delimiter                                                                                                                  |

| FCS                                                 | Frame Check Sequence                                                                                                                     |

| FDX                                                 | Full-Duplex                                                                                                                              |

| FEF                                                 | Far End Fault                                                                                                                            |

| FLP                                                 | Fast Link Pulse                                                                                                                          |

| FX                                                  | Fiber                                                                                                                                    |

| HDX                                                 | Half-Duplex                                                                                                                              |

| HIZ                                                 | High Impedance                                                                                                                           |

| I/G                                                 | Individual/Group                                                                                                                         |

| IETF                                                | Internet Engineering Task Force                                                                                                          |

| IPG                                                 | Interpacket Gap                                                                                                                          |

| IREF                                                | Reference Current                                                                                                                        |

| L/T                                                 | Length and Type                                                                                                                          |

| LSB                                                 | Least Significant Bit                                                                                                                    |

| MIB      | Management Information Base                         |

|----------|-----------------------------------------------------|

| MLT3     | Multilevel Transmission (3 levels)                  |

| MSB      | Most Significant Bit                                |

| mV       | millivolt                                           |

| NLP      | Normal Link Pulse                                   |

| NRZI     | Nonreturn to Zero Inverted                          |

| NRZ      | Nonreturn to Zero                                   |

| OP       | Opcode                                              |

| PCB      | Printed Circuit Board                               |

| рF       | picofarad                                           |

| PRE      | Preamble                                            |

| R/LH     | Read Latched High                                   |

| R/LHI    | Read Latched High with Interrupt                    |

| R/LL     | Read Latched Low                                    |

| R/LLI    | Read Latched Low with Interrupt                     |

| R/LT     | Read Latched Transition                             |

| R/LTI    | Read Latched Transition with Interrupt              |

| R/WSC    | Read/Write Self Clearing                            |

| RFC      | Request for Comments                                |

| RJ-45    | Registered Jack-45                                  |

| RMON     | Remote Monitoring                                   |

| SA       | Start Address or Station Address                    |

| SFD      | Start of Frame Delimiter                            |

| SNMP     | Simple Network Management Protocol                  |

| SOI      | Start of Idle                                       |

| Split-32 | Independent 32-bit input and output busses; one for |

| 00111 02 | transmit and one for receive                        |

| SSD      | Start of Stream Delimiter                           |

| STP      | Shielded Twisted Pair                               |

| TP       | Twisted Pair                                        |

| μH       | microHenry                                          |

| μP       | microprocessor                                      |

| UTP      | Unshielded Twisted Pair                             |

|          |                                                     |

#### **Conventions Used in This Manual**

The first time a word or phrase is defined in this manual, it is *italicized*.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive. Signals that are active LOW end in an "n."

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

# Contents

| Chapter 1 | Introduction |           |                              |      |

|-----------|--------------|-----------|------------------------------|------|

|           | 1.1          | Overvi    | ew                           | 1-1  |

|           | 1.2          | Featur    | es                           | 1-2  |

| Chapter 2 | Fun          | ctional E | Description                  |      |

| -         | 2.1          | Overvi    | ew                           | 2-2  |

|           | 2.2          | Transn    | nit Data Path                | 2-2  |

|           | 2.3          | Receiv    | e Data Path                  | 2-6  |

|           | 2.4          | Regist    | er Structure                 | 2-6  |

|           | 2.5          | Ethern    | et Frame Format              | 2-6  |

|           |              | 2.5.1     | Preamble and SFD             | 2-7  |

|           |              | 2.5.2     | Destination Address          | 2-7  |

|           |              | 2.5.3     | Source Address               | 2-7  |

|           |              | 2.5.4     | Length/Type Field            | 2-7  |

|           |              | 2.5.5     | Data                         | 2-8  |

|           |              | 2.5.6     | Frame Check Sequence (FCS)   | 2-8  |

|           |              | 2.5.7     | Interpacket Gap (IPG)        | 2-8  |

|           | 2.6          | Syster    | n Interface                  | 2-8  |

|           |              | 2.6.1     | Data Format and Bit Order    | 2-9  |

|           |              | 2.6.2     | Transmit Timing              | 2-9  |

|           |              | 2.6.3     | Receive Timing               | 2-11 |

|           |              | 2.6.4     | Bus Width                    | 2-14 |

|           |              | 2.6.5     | System Interface Disable     | 2-14 |

|           | 2.7          | Transn    | nit MAC                      | 2-15 |

|           |              | 2.7.1     | Preamble and SFD Generation  | 2-15 |

|           |              | 2.7.2     | AutoPad                      | 2-15 |

|           |              | 2.7.3     | CRC Generation               | 2-15 |

|           |              | 2.7.4     | Interpacket Gap              | 2-16 |

|           |              | 2.7.5     | MAC Control Frame Generation | 2-17 |

| 2.8  | Receive  | e MAC                        | 2-17 |

|------|----------|------------------------------|------|

|      | 2.8.1    | Preamble and SFD Stripping   | 2-17 |

|      | 2.8.2    | CRC Stripping                | 2-17 |

|      | 2.8.3    | Unicast Address Filter       | 2-18 |

|      | 2.8.4    | Multicast Address Filter     | 2-18 |

|      | 2.8.5    | Broadcast Address Filter     | 2-19 |

|      | 2.8.6    | Reject or Accept All Packets | 2-20 |

|      | 2.8.7    | Frame Validity Checks        | 2-20 |

|      | 2.8.8    | Maximum Packet Size          | 2-21 |

|      | 2.8.9    | MAC Control Frame Check      | 2-21 |

| 2.9  | Transmi  | it FIFO                      | 2-22 |

|      | 2.9.1    | AutoSend                     | 2-22 |

|      | 2.9.2    | Watermarks                   | 2-22 |

|      | 2.9.3    | TX Underflow                 | 2-23 |

|      | 2.9.4    | TX Overflow                  | 2-23 |

|      | 2.9.5    | Link Down FIFO Flush         | 2-24 |

| 2.10 | Receive  | e FIFO                       | 2-24 |

|      | 2.10.1   | Watermarks                   | 2-24 |

|      | 2.10.2   | RX Overflow                  | 2-25 |

|      | 2.10.3   | RX Underflow                 | 2-25 |

| 2.11 | 8B10B    | PCS                          | 2-25 |

|      | 2.11.1   | 8B10B Encoder                | 2-26 |

|      | 2.11.2   | 8B10B Decoder                | 2-28 |

|      | 2.11.3   | Start of Packet              | 2-29 |

|      | 2.11.4   | End Of Packet                | 2-30 |

|      | 2.11.5   | Idle                         | 2-30 |

|      | 2.11.6   | Receive Word Synchronization | 2-31 |

|      | 2.11.7   | AutoNegotiation              | 2-31 |

| 2.12 | 10-Bit F | PHY Interface                | 2-31 |

|      | 2.12.1   | Data Format and Bit Order    | 2-32 |

|      | 2.12.2   | Transmit                     | 2-32 |

|      | 2.12.3   | Receive                      | 2-32 |

|      | 2.12.4   | Lock To Reference            | 2-33 |

|      | 2.12.5   | PHY Loopback                 | 2-33 |

|      | 2.12.6   | Signal Detect                | 2-33 |

|      | 2.12.7   | TBC Disable                  | 2-34 |

| 2.13 | Packet   | Discard                      | 2-34 |

|      | 2.13.1   | Transmit Discards            | 2-34 |

|           |                              | 2.13.2                           | Receive Discards                   | 2-35 |

|-----------|------------------------------|----------------------------------|------------------------------------|------|

|           |                              | 2.13.3                           | Discard Output Indication          | 2-36 |

|           |                              | 2.13.4                           | AutoClear Mode                     | 2-36 |

|           |                              | 2.13.5                           | AutoAbort Mode                     | 2-36 |

|           | 2.14                         | Receive                          | e Status Word                      | 2-37 |

|           |                              | 2.14.1                           | Format                             | 2-37 |

|           |                              | 2.14.2                           | Append Options                     | 2-38 |

|           |                              | 2.14.3                           | Status Word for Discarded Packets  | 2-38 |

|           |                              | 2.14.4                           | Status Word for RXABORT Packets    | 2-38 |

|           | 2.15                         | AutoNe                           | gotiation                          | 2-39 |

|           |                              | 2.15.1                           | Next Page                          | 2-40 |

|           |                              | 2.15.2                           | Negotiation Status                 | 2-41 |

|           |                              | 2.15.3                           | AutoNegotiation Restart            | 2-41 |

|           |                              | 2.15.4                           | AutoNegotiation Enable             | 2-42 |

|           |                              | 2.15.5                           | Link Indication                    | 2-42 |

|           | 2.16                         | Flow C                           | ontrol                             | 2-42 |

|           | 2.17                         | MAC C                            | ontrol Frames                      | 2-42 |

|           |                              | 2.17.1                           | Automatic Pause Frame Generation   | 2-43 |

|           |                              | 2.17.2                           | Transmitter Pause Disable          | 2-44 |

|           |                              | 2.17.3                           | Pass Through to FIFO               | 2-44 |

|           |                              | 2.17.4                           | Reserved Multicast Address Disable | 2-46 |

|           |                              | 2.17.5                           | MAC Control Frame AutoSend         | 2-46 |

|           | 2.18                         | Reset                            |                                    | 2-46 |

|           | 2.19                         | Counte                           | rs                                 | 2-47 |

|           |                              | 2.19.1                           | Counter Half Full                  | 2-57 |

|           |                              | 2.19.2                           | Counter Reset On Read              | 2-57 |

|           |                              | 2.19.3                           | Counter Rollover                   | 2-58 |

|           |                              | 2.19.4                           | Counter Maximum Packet Size        | 2-58 |

|           |                              | 2.19.5                           | Counter Reset                      | 2-58 |

|           | 2.20                         | Loopba                           | ick                                | 2-59 |

|           | 2.21                         | Test Mo                          | odes                               | 2-59 |

| Chapter 3 | Signa                        | al Descr                         | iptions                            |      |

|           | 3.1 System Interface Signals |                                  |                                    | 3-3  |

|           | 3.2                          | 3.2 10-Bit PHY Interface Signals |                                    | 3-7  |

|           | 3.3                          | Registe                          | er Interface Signals               | 3-8  |

|           | 3.4                          | -                                | neous Signals                      | 3-9  |

|           | 3.5                          |                                  | Supply Signals                     | 3-10 |

|           |                              |                                  |                                    |      |

| Chapter 4 | Regi | sters    |                                                |     |

|-----------|------|----------|------------------------------------------------|-----|

|           | 4.1  | Register | Interface                                      | 4-1 |

|           |      | 4.1.1    | Bit Types                                      | 4-2 |

|           |      | 4.1.2    | Interrupt                                      | 4-: |

|           |      | 4.1.3    | Register Structure                             | 4-4 |

|           | 4.2  | Register | Addresses                                      | 4-4 |

|           | 4.3  | Register | Definitions                                    | 4-  |

|           |      | 4.3.1    | Register 0-MAC Address 1                       | 4-  |

|           |      | 4.3.2    | Register 1-MAC Address 2                       | 4-1 |

|           |      | 4.3.3    | Register 2-MAC Address 3                       | 4-1 |

|           |      | 4.3.4    | Register 3-MAC Address Filter 1                | 4-1 |

|           |      | 4.3.5    | Register 4-MAC Address Filter 2                | 4-1 |

|           |      | 4.3.6    | Register 5-MAC Address Filter 3                | 4-1 |

|           |      | 4.3.7    | Register 6-MAC Address Filter 4                | 4-1 |

|           |      | 4.3.8    | Register 7-Configuration 1                     | 4-1 |

|           |      | 4.3.9    | Register 8-Configuration 2                     | 4-1 |

|           |      | 4.3.10   | Register 9-Configuration 3                     | 4-1 |

|           |      | 4.3.11   | Register 10-Configuration 4                    | 4-2 |

|           |      | 4.3.12   | Register 11-Status 1                           | 4-2 |

|           |      | 4.3.13   | Register 14-Status Mask 1                      | 4-2 |

|           |      | 4.3.14   | Register 17-Transmit FIFO Threshold            | 4-2 |

|           |      | 4.3.15   | Register 18-Receive FIFO Threshold             | 4-2 |

|           |      | 4.3.16   | Register 19-Flow Control 1                     | 4-2 |

|           |      | 4.3.17   | Register 20-Flow Control 2                     | 4-2 |

|           |      | 4.3.18   | Register 21-AutoNegotiation Base Page Transmit | 4-2 |

|           |      | 4.3.19   | Register 22-AutoNegotiation Base Page Receive  | 4-2 |

|           |      | 4.3.20   | Register 23-AutoNegotiation Next Page Transmit | 4-3 |

|           |      | 4.3.21   | Register 24-AutoNegotiation Next Page Receive  | 4-3 |

|           |      | 4.3.22   | Register 32-Device ID                          | 4-3 |

|           |      | 4.3.23   | Register 112–115-Counter Half Full 1–4         | 4-3 |

|           |      | 4.3.24   | Registers 120–123-Counter Half Full Mask 1–4   | 4-3 |

|           |      | 4.3.25   | Registers 128–233-Counter 1–53                 | 4-3 |

#### Chapter 5

### **Application Information**

| 5.1 | Typical Ethernet Port | 5-2 |

|-----|-----------------------|-----|

| 5.2 | 10-Bit PHY Interface  | 5-2 |

|           |     | 5.2.1      | External Physical Layer Devices        | 5-2  |

|-----------|-----|------------|----------------------------------------|------|

|           |     | 5.2.2      | Printed Circuit Board Layout           | 5-3  |

|           | 5.3 | System     | n Interface                            | 5-3  |

|           |     | 5.3.1      | Watermarks                             | 5-3  |

|           |     | 5.3.2      | PCB Layout                             | 5-5  |

|           | 5.4 | Reset      |                                        | 5-5  |

|           | 5.5 | Loopba     | ack                                    | 5-6  |

|           | 5.6 | AutoNe     | egotiation                             | 5-7  |

|           |     | 5.6.1      | AutoNegotiation at Power Up            | 5-8  |

|           |     | 5.6.2      | Negotiating with a Non-AutoNegotiation |      |

|           |     |            | Capable Device                         | 5-9  |

|           | 5.7 | Manag      | ement Counters                         | 5-9  |

|           | 5.8 | TX Pac     | cket and Octet Counters                | 5-16 |

|           | 5.9 | Power      | Supply Decoupling                      | 5-16 |

| Chapter 6 | Spe | cificatior | IS                                     |      |

|           | 6.1 | Absolu     | te Maximum Ratings                     | 6-1  |

|           | 6.2 | DC Ele     | ectrical Characteristics               | 6-2  |

|           | 6.3 | AC Ele     | ctrical Characteristics                | 6-3  |

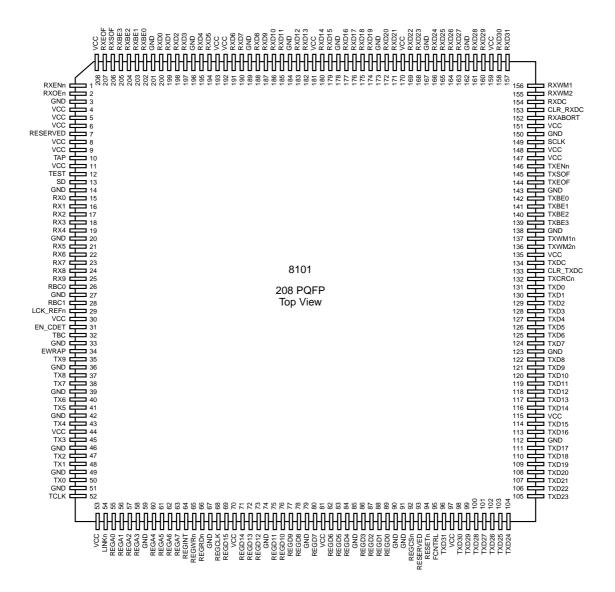

|           | 6.4 | 8101 2     | 08-pin PQFP Pinout and Pin Listing     | 6-17 |

|           | 6.5 | 8104 2     | 08-Pin BGA Pinout and Pin Listing      | 6-19 |

|           | 6.6 | Packag     | e Mechanical Dimensions                | 6-21 |

|           |     |            |                                        |      |

#### **Customer Feedback**

# Figures

| 2.1 | 8101/8104 Block Diagram                          | 2-3  |

|-----|--------------------------------------------------|------|

| 2.2 | Ethernet MAC Frame Format                        | 2-4  |

| 2.3 | Frame Formats and Bit Ordering                   | 2-5  |

| 2.4 | Little Endian vs. Big Endian Format              | 2-9  |

| 2.5 | RXSOF/RXEOF Position                             | 2-13 |

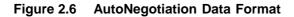

| 2.6 | AutoNegotiation Data Format                      | 2-39 |

| 2.7 | Autogenerated Pause Frame Format                 | 2-45 |

| 3.1 | 8101/8104 Interface Diagram                      | 3-2  |

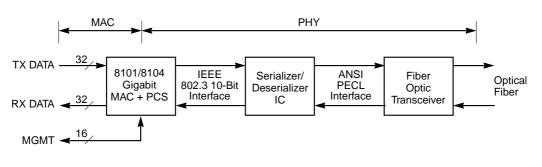

| 5.1 | Gigabit Ethernet Switch Port Using the 8101/8104 | 5-2  |

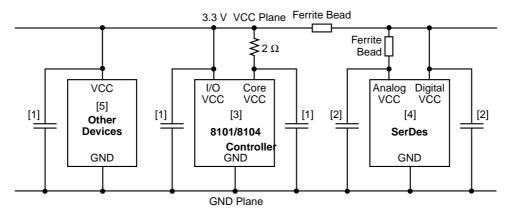

| 5.2 | Decoupling Recommendations                       | 5-17 |

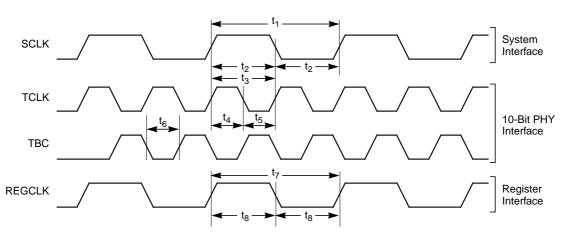

| 6.1 | Input Clock Timing                               | 6-4  |

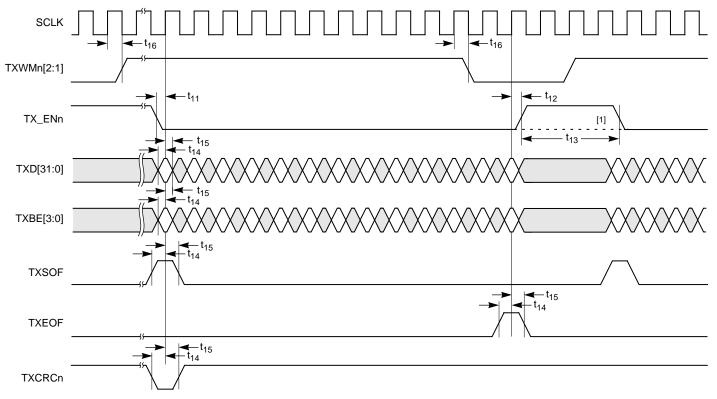

| 6.2  | Transmit System Interface Timing              | 6-6  |

|------|-----------------------------------------------|------|

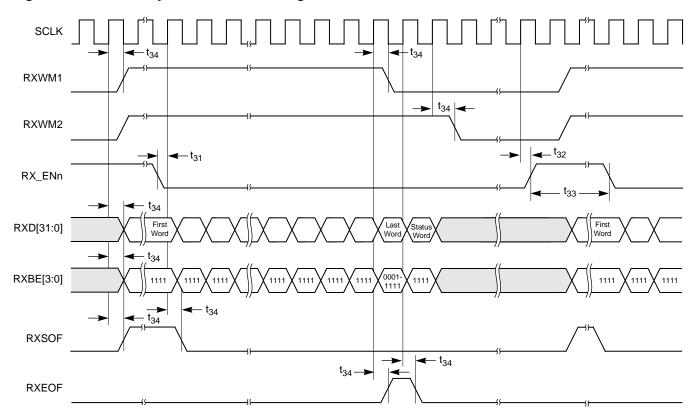

| 6.3  | Receive System Interface Timing               | 6-8  |

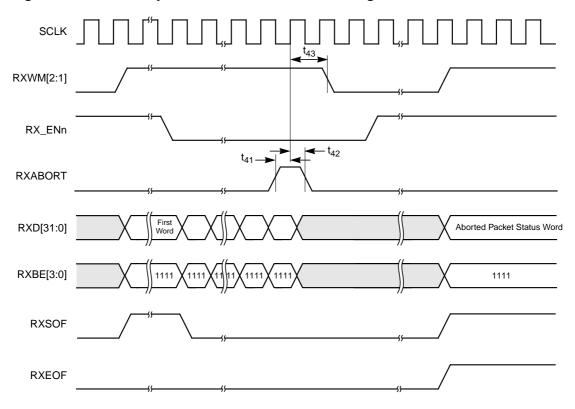

| 6.4  | Receive System Interface RXABORT Timing       | 6-9  |

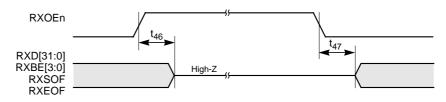

| 6.5  | Receive System Interface RXOEn Timing         | 6-9  |

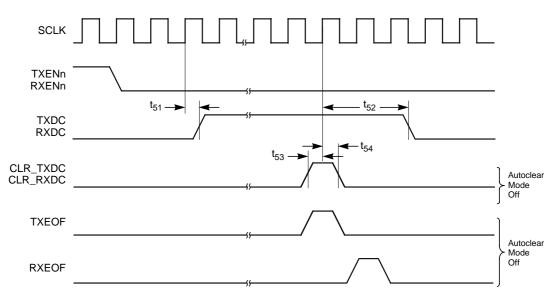

| 6.6  | System Interface RXDC/TXDC Timing             | 6-10 |

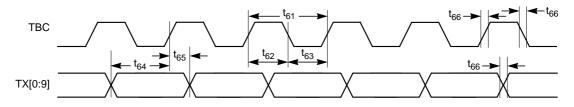

| 6.7  | Transmit 10-Bit PHY Interface Timing          | 6-11 |

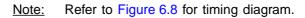

| 6.8  | Receive 10-Bit PHY Interface Timing           | 6-12 |

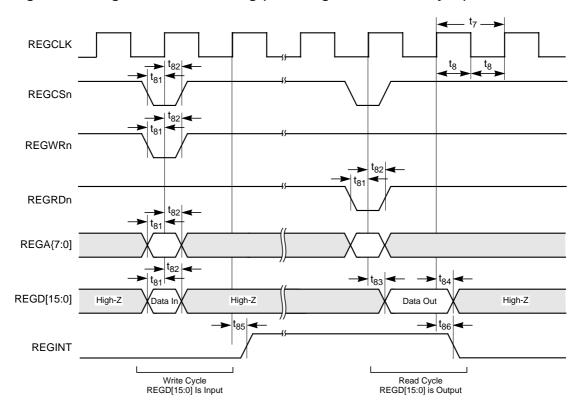

| 6.9  | Register Interface Timing (Excluding Counter  |      |

|      | Read Cycle)                                   | 6-14 |

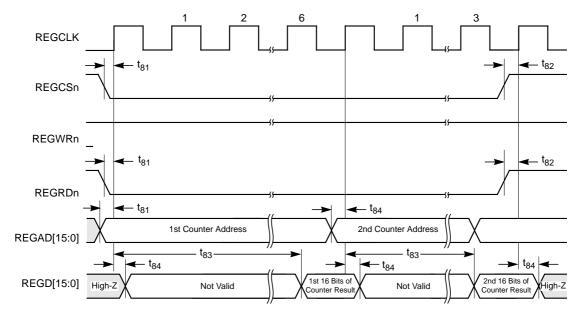

| 6.10 | Register Interface Timing, Counter Read Cycle |      |

|      | (of the Same Counter)                         | 6-15 |

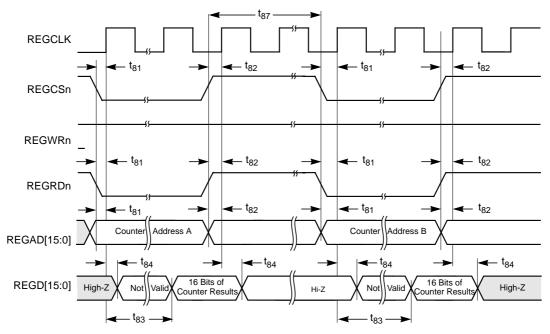

| 6.11 | Register Interface Timing, Counter Read Cycle |      |

|      | (Between Different Counters)                  | 6-16 |

| 6.12 | 8101 208-Pin PQFP Pinout                      | 6-17 |

| 6.13 | 8104 208-Pin BGA Pinout                       | 6-19 |

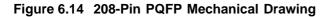

| 6.14 | 208-Pin PQFP Mechanical Drawing               | 6-21 |

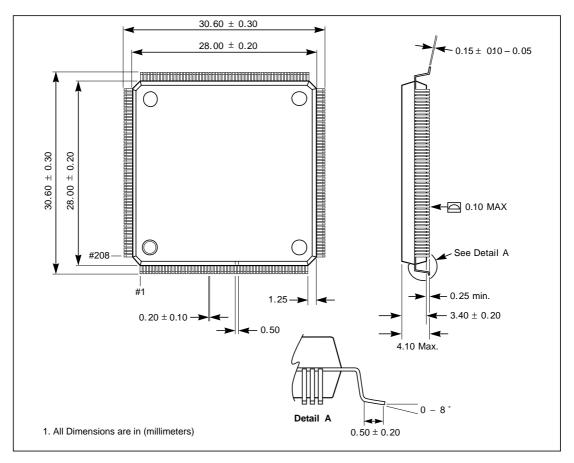

| 6.15 | 208 mini-BGA (HG) Mechanical Drawing          | 6-22 |

|      |                                               |      |

#### Tables

| 2.1  | Length/Type Field Definition            | 2-8  |

|------|-----------------------------------------|------|

| 2.2  | Byte Enable Pin vs. Valid Byte Position | 2-10 |

| 2.3  | TXRC Bit and TXCRCn Pin Logic           | 2-16 |

| 2.4  | Transmit IPG Selection                  | 2-16 |

| 2.5  | Multicast Address Filter Map            | 2-19 |

| 2.6  | Receive Maximum Packet Size Selection   | 2-21 |

| 2.7  | 8B10B Coding Table                      | 2-27 |

| 2.8  | 10B Defined Ordered Sets                | 2-28 |

| 2.9  | Transmit Discard Conditions             | 2-34 |

| 2.10 | Receive Discard Conditions              | 2-35 |

| 2.11 | Receive Status Word Definition          | 2-37 |

| 2.12 | AutoNegotiation Status Bits             | 2-41 |

| 2.13 | Reset Description                       | 2-47 |

| 2.14 | Counter Definition                      | 2-49 |

| 2.15 | Counter Maximum Packet Size Selection   | 2-58 |

| 4.1  | Register Bit Type Definition            | 4-3  |

| 4.2  | Register Address                        | 4-4  |

| 5.1  | Compatible SerDes Devices               | 5-3  |

| 5.2  | Reset Procedure                         | 5-6  |

| 5.3 | SerDes Loopback Procedure                            | 5-7  |

|-----|------------------------------------------------------|------|

| 5.4 | AutoNegotiation Power Up Procedure                   | 5-8  |

| 5.5 | MIB Objects vs. Counter Location For RMON Statistics |      |

|     | Group MIB (RFC 1757)                                 | 5-10 |

| 5.6 | MIB Objects vs. Counter Location For SNMP Interface  |      |

|     | Group MIB (RFC 1213 and 1573)                        | 5-11 |

| 5.7 | MIB Objects vs. Counter Location For Ethernet-Like   |      |

|     | Group MIB (RFC 1643)                                 | 5-13 |

| 5.8 | MIB Objects vs. Counter Location For Ethernet MIB    |      |

|     | (IEEE 802.3z, Clause 30)                             | 5-14 |

| 6.1 | DC Electrical Characteristics                        | 6-2  |

| 6.2 | Input Clock Timing Characteristics                   | 6-4  |

| 6.3 | Transmit System Interface Timing Characteristics     | 6-5  |

| 6.4 | Receive System Interface Timing Characteristics      | 6-7  |

| 6.5 | System Interface TXDC/RXDC Timing Characteristics    | 6-10 |

| 6.6 | Transmit 10-Bit PHY Interface Timing Characteristics | 6-11 |

| 6.7 | Receive 10-Bit PHY Interface Timing Characteristics  | 6-12 |

| 6.8 | Register Interface Timing Characteristics            | 6-13 |

# Chapter 1 Introduction

This chapter contains a brief introduction to the 8101/8104 Gigabit Ethernet Controller. It consists of the following sections:

- Section 1.1, "Overview"

- Section 1.2, "Features"

## 1.1 Overview

The 8101/8104 Gigabit Ethernet Controller is a complete media access controller (MAC sublayer) with integrated coding logic for fiber and short haul copper media (8 bit/10 bit Physical Coding Sublayer) (8B10B PCS) for 1000 Mbits/s Gigabit Ethernet systems.

The 8104 is functionally the same as the 8101 except that the 8104 is in a 208-pin Ball Grid Array (BGA) package and the 8101 is in a 208-pin Plastic Quad Flat Pack (PQFP) package

The Controller consists of a 32-bit system interface, receive/transmit First In, First Out (FIFO) buffers, a full-duplex Ethernet Media Access Controller (MAC), an 8 bit/10 bit PCS, a 10-bit Physical Layer Device (PHY) interface, and a 16-bit register interface. The controller also contains all the necessary circuitry to implement the IEEE 802.3x Flow Control Algorithm. Flow control messages can be sent automatically without host intervention.

The controller contains 53 counters which satisfy the management objectives of the Remote Monitoring (RMON) Statistics Group MIB, (RFC 1757), Simple Network Management Protocol (SNMP) Interfaces Group (RFC 1213 and 1573), Ethernet-Like Group MIB (RFC 1643), and Ethernet MIB (IEEE 802.3z Clause 30). The controller also contains 136

internal 16-bit registers that can be accessed through the register interface. These registers contain configuration inputs, status outputs, and management counter results.

The 8101/8104 is ideal as an Ethernet controller for Gigabit Ethernet switch ports, uplinks, backbones, and adapter cards.

## 1.2 Features

The 8101/8104 provides the following features.

- Pin-compatible upgrade of 8100

- Combined Ethernet MAC and 8B10B PCS

- 1000 Mbits/s data rate

- 64-bit, 66 MHz external bus interface (4 Gbits/s bandwidth)

- 10-bit interface to external SerDes chip

- 16-bit interface to internal registers and management counters

- Full RMON, SNMP, and Ethernet management counter support

- Independent receive and transmit FIFOs with programmable watermarks

- 16 Kbytes receive FIFO size

- 4 Kbytes transmit FIFO size

- AutoNegotiation algorithm on chip

- Full duplex only

- Flow control per IEEE 802.3x

- Automatic CRC generation and checking

- Automatic packet error discarding

- Programmable transmit start threshold

- Interrupt capability

- Support for fiber and short haul copper media

- 3.3 V power supply, 5 V tolerant inputs

- IEEE 802.3 and 802.3z specification compliant

# Chapter 2 Functional Description

This chapter provides a high level description of the 8101/8104 Gigabit Ethernet Controller and consists of the following sections:

- Section 2.1, "Overview"

- Section 2.2, "Transmit Data Path"

- Section 2.3, "Receive Data Path"

- Section 2.4, "Register Structure"

- Section 2.5, "Ethernet Frame Format"

- Section 2.6, "System Interface"

- Section 2.7, "Transmit MAC"

- Section 2.8, "Receive MAC"

- Section 2.9, "Transmit FIFO"

- Section 2.10, "Receive FIFO"

- Section 2.11, "8B10B PCS"

- Section 2.12, "10-Bit PHY Interface"

- Section 2.13, "Packet Discard"

- Section 2.14, "Receive Status Word"

- Section 2.15, "AutoNegotiation"

- Section 2.16, "Flow Control"

- Section 2.17, "MAC Control Frames"

- Section 2.18, "Reset"

- Section 2.19, "Counters"

- Section 2.20, "Loopback"

- Section 2.21, "Test Modes"

## 2.1 Overview

The 8101/8104 is a complete Media Access Controller (MAC) sublayer with integrated coding logic for fiber and short haul copper media (8B10B PCS sublayer) for 1000 Mbits/s Gigabit Ethernet systems. The controller has seven main sections:

- System interface

- FIFOs

- MAC

- 8B10B PCS

- 10-bit PHY interface

- Register interface.

- Management counters

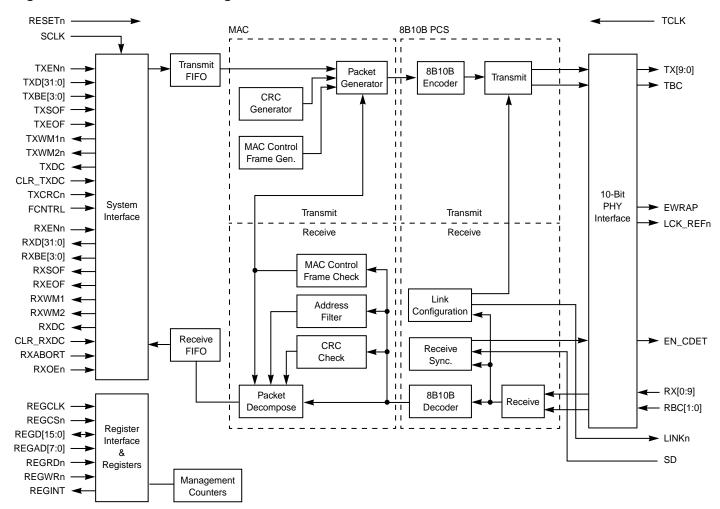

A block diagram is shown in Figure 2.1.

The controller has a transmit data path and a receive data path. The transmit data path goes in the system interface and out the 10-bit PHY interface, as shown in the top half of Figure 2.1. The receive data path goes in the 10-bit PHY interface and out the system interface, as shown in the bottom half of Figure 2.1.

# 2.2 Transmit Data Path

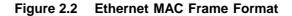

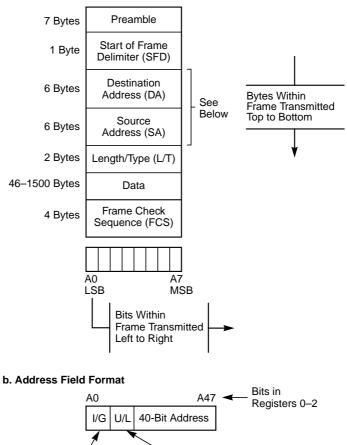

Data is input to the system from an external bus. The data is then sent to the transmit FIFO. The transmit FIFO provides temporary storage of the data until it is sent to the MAC transmit section. The transmit MAC formats the data into an Ethernet packet according to IEEE 802.3 specification as shown in Figure 2.2. The transmit MAC also generates MAC control frames and includes logic for AutoNegotiation. The Ethernet frame packet is then sent to the 8B10B PCS.

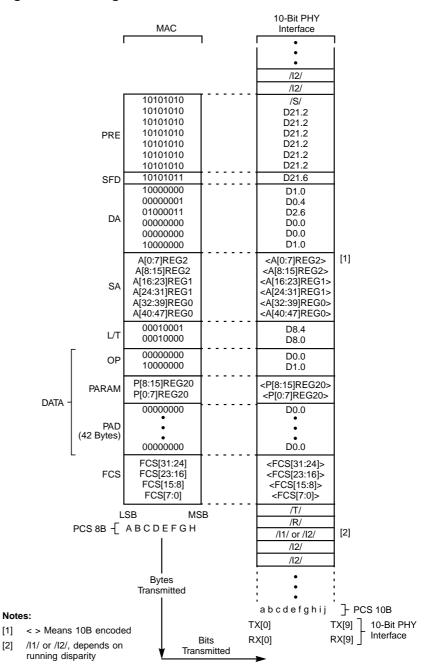

The 8B10B PCS encodes the data and adds appropriate framing delimiters to create 10-bit symbols as specified in IEEE 802.3 and shown in Figure 2.3. The 10-bit symbols are then sent to the 10-bit PHY interface for transmission to an external PHY device.

Figure 2.1 8101/8104 Block Diagram

2-3

1 = Broadcast0 = Multicast

1 = Multicast or Broadcast

0 = Unicast

#### Figure 2.3 Frame Formats and Bit Ordering

# 2.3 Receive Data Path

The 10-bit PHY interface receives incoming encoded data from an external PHY device. The incoming encoded data must be encoded in the 10-bit PHY format specified in IEEE 802.3z, as shown in Figure 2.3. The incoming encoded data is then sent to the receive 8B10B PCS block, which strips off the framing delimiters, decodes the data, and converts the encoded data into an Ethernet packet according to the IEEE 802.3 specifications, as shown in Figure 2.2. The Ethernet packet data is then sent to the receive MAC section.

The receive MAC section disassembles the packet, checks the validity of the packet against certain error criteria and address filters, and checks for MAC control frames. The receive MAC then sends valid packets to the receive FIFO. The receive FIFO provides temporary storage of data until it is demanded by the system interface. The system interface outputs the data to an external bus.

## 2.4 Register Structure

The controller has 136 internal 16-bit registers. 22 registers are available for setting configuration inputs and reading status outputs. The remaining 114 registers are associated with the management counters.

The register interface is a separate internal register bidirectional 16 bit data bus to set configuration inputs, read status outputs, and access management counters.

The location of all registers is described in the Register Addressing Table in Section 4.2, "Register Addresses". The description of each bit for each register is described in Section 4.3.1 through Section 4.3.25.

# 2.5 Ethernet Frame Format

Information in an Ethernet network is transmitted and received in packets or frames. The basic function of the controller is to process Ethernet frames. An Ethernet frame is defined in IEEE 802.3 and consists of a preamble, start of frame delimiter (SFD), destination address (DA), source address (SA), length/type field (L/T), data, frame check sequence (FCS), and interpacket gap (IPG). The format for the Ethernet frame is shown in Figure 2.2.

An Ethernet frame is specified by IEEE 802.3 to have a minimum length of 64 bytes and a maximum length of 1518 bytes, exclusive of the preamble and SFD. Packets that are less than 64 bytes or greater than 1518 bytes are referred to as undersize and oversize packets, respectively.

#### 2.5.1 Preamble and SFD

The preamble and SFD is a combined 64-bit field consisting of 62 alternating ones and zeros followed by a 0b11 end of preamble indicator. The first 56-bits of ones and zeros are considered to be the preamble, and the last 8 bits (0b10101011) are considered to be the SFD.

#### 2.5.2 Destination Address

The destination address is a 48-bit field containing the address of the station(s) to which the frame is directed. The format of the address field is the same as defined in IEEE 802.3 and shown in Figure 2.2 b. The destination address can be either a unicast address to a specific station, a multicast address to a group of stations, or a broadcast address to all stations. The first and second bits determine whether an address is unicast, multicast or broadcast, and the remaining 46 bits are the actual address bits, as shown in Figure 2.2 b.

#### 2.5.3 Source Address

The source address is a 48-bit field containing the specific station address from which the frame originated. The format of the address field is the same as defined in IEEE 802.3 and shown in Figure 2.2 b.

#### 2.5.4 Length/Type Field

The 16-bit length/type field takes on the meaning of either packet length or packet type, depending on its numeric value, as described in Table 2.1.

| Length/Type<br>Field Value<br>(Decimal) | Length<br>or Type | Definition                                            |  |

|-----------------------------------------|-------------------|-------------------------------------------------------|--|

| 0–1500                                  | Length            | Total number of bytes in data field minus any padding |  |

| 1501–1517                               | Neither           | Undefined                                             |  |

| ≥ 1518                                  | Туре              | Frame type                                            |  |

#### Table 2.1 Length/Type Field Definition

#### 2.5.5 Data

The data is a 46–1500 byte field containing the actual data to be transmitted between two stations. If the actual data is less than 46 bytes, extra zeros are added to increase the data field to the 46 byte minimum size. Adding these extra zeros is referred to as padding.

#### 2.5.6 Frame Check Sequence (FCS)

The FCS is a 32-bit cyclic redundancy check (CRC) value computed on the entire frame, exclusive of preamble and SFD. The FCS algorithm is defined in IEEE 802.3. The FCS is appended to the end of the frame and determines frame validity.

#### 2.5.7 Interpacket Gap (IPG)

The IPG is the time interval between packets. The minimum IPG value is 96 bits, where 1 bit = 1 ns for Gigabit Ethernet. There is no maximum IPG limit.

# 2.6 System Interface

The system interface is a 64-bit wide data interface consisting of separate 32-bit data busses for transmit and receive.

#### 2.6.1 Data Format and Bit Order

The format of the data word on TXD[31:0] and RXD[31:0] and its relationship to the MAC frame format and 10-bit PHY interface format is

shown in Figure 2.3. Note that the controller can be programmed to append an additional 32-bit status word to the end of the receive packet. Refer to Section 2.14, "Receive Status Word," for more details on this status word.

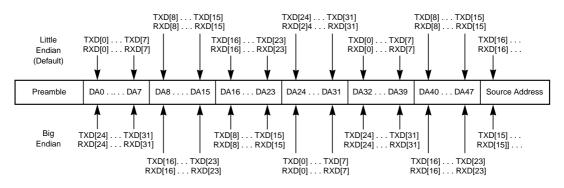

To program the byte ordering of the TXD and RXD data bits, set the endian bit in "Register 10–Configuration 4," Section 4.3.11. The byte order shown in Figure 2.4 is with the little endian format mode (default). If the controller is placed in big endian format, the byte order shown in Figure 2.4 is reversed, DA[0:7] occurs on pins RXD[24:31], DA[24:31] occurs on pins RXD[0:7]and so on. The endian bit affects all bytes in the frame including the receive status word (if appended). The difference between little endian and big endian format is illustrated in Figure 2.4.

#### Figure 2.4 Little Endian vs. Big Endian Format

#### 2.6.2 Transmit Timing

The transmit portion of the system interface consists of 45 signals: 32 transmit data input bits (TXD[31:0]), one transmit enable (TXENn), four transmit byte enable inputs (TXBE[3:0]), two transmit start of frame and end of frame inputs (TXSOF and TXEOF), two transmit FIFO watermark outputs (TXWM1n and TXWM2n), one transmit discard output (TXDC), one transmit discard clear input (CLR\_TXDC), one transmit CRC enable input (TXCRCn), and one flow control enable input (FCNTRL). All receive and transmit data is clocked in and out on the rising edge of the system clock, SCLK. SCLK must operate between 33–66 MHz.

The SCLK input needs to be continuously input to the controller at 33–66 MHz. When TXENn is deasserted, the transmit interface is not selected and subsequently, the controller accepts no input data from the

transmit system interface inputs. When TXENn is asserted, a data word on the TXD[31:0] input is clocked into the transmit FIFO on each rising edge of the SCLK clock input. Multiple packets may be clocked in on one TXENn assertion. The TXD[31:0] input data is a 32-bit wide packet data whose format and relationship to the MAC packet and 10-bit PHY data is described in Figure 2.3.

The TXBE[3:0] pins determine which bytes of the 32-bit TXD[31:0] data word contain valid data. TXBE[3:0] are clocked in on the rising edge of SCLK along with each TXD[31:0] data word. The correspondence between the byte enable inputs and the valid bytes of each data word on TXD[31:0] is defined in Table 2.2. Any logic combination of TXBE[3:0] inputs is allowed, with the one exception that TXBE[3:0] must not be 0b0000 on the SCLK cycle when TXSOF or TXEOF is asserted.

Table 2.2

Byte Enable Pin vs. Valid Byte Position

| TXBE[3:0]/RXBE[3:0] Byte<br>Enable Pins | Valid Bytes on<br>TXD[31:0]/RXD[31:0] Pins |  |

|-----------------------------------------|--------------------------------------------|--|

| TXBE[3]/RXBE[3] Asserted                | TXD[31:24]/RXD[31:24]                      |  |

| TXBE[2]/RXBE[2] Asserted                | TXD[23:16]/RXD[23:16]                      |  |

| TXBE[1]/RXBE[1] Asserted                | TXD[15:8]/RXD[15:8]                        |  |

| TXBE[0]/RXBE[0] Asserted                | TXD[7:0]/RXD[7:0]                          |  |

The TXSOF and TXEOF signals indicate to the controller which data words start and end the Ethernet data packet, respectively. These signals are input on the same SCLK rising edge as the first and last word of the data packet.

The TXWM1n and TXWM2n signals indicate when the transmit FIFO has exceeded the programmable watermark thresholds. The controller asserts the watermarks on the rising edge of SCLK, depending on the fullness of the transmit FIFO. Refer to Section 2.9, "Transmit FIFO," for more details on these watermarks.

TXDC is a transmit packet discard output. TXDC is asserted every time the transmission of the packet being input on the system interface was halted and the packet discarded due to some error. This signal is latched HIGH. It is cleared when the clearing signal, CLR\_TXDC, is asserted or cleared automatically if the controller is placed in the AutoClear mode. See Section 2.13, "Packet Discard," for more details on discards and TXDC.

TXCRCn is an input that can enable the internal generation and appending of the 4-byte CRC value onto the end of the data packet. TXCRCn is sampled on the rising edge of SCLK and has to be asserted at the beginning of the packet, coincident with TXSOF, to remove or add the CRC to that packet. Setting the transmit CRC enable bit (TXCRC) in the Configuration 1 register also enables CRC generation. Refer to Section 2.7.3, "CRC Generation" for more details on CRC generation and the interaction between TXCRCn and the TXCRC bit.

FCNTRL is an input that causes the automatic generation and transmission of a MAC control pause frame. FCNTRL is input on the rising edge of SCLK. See Section 2.17, "MAC Control Frames," for more details about this feature.

#### 2.6.3 Receive Timing

The receive portion of the system interface consists of 45 signals:

- 32 receive output data bits (RXD[31:0])

- One receive enable input (RXENn)

- Four receive byte enable outputs (RXBE[3:0])

- One receive start of frame and one end of frame outputs (RXSOF and RXEOF)

- Two receive FIFO watermark outputs (RXWM1 and RXWM2)

- One receive discard output (RXDC)

- One receive discard clear input (CLR\_RXDC)

- One receive packet abort input (RXABORT)

- One receive output enable (RXOEn)

All receive and transmit data is clocked in and out with the system clock, SCLK, which must operate between 33–66 MHz.

The SCLK input must continuously operate at 33–66 MHz. When RXENn is deasserted, the receive interface is not selected and, subsequently, no data from the receive FIFO can be output over the system interface. If the receive watermarks RXWM1 and RXWM2 are asserted while RXENn is deasserted, the next data word from the receive FIFO appears on the RXD[31:0] outputs until RXENn is asserted. When RXENn is asserted, a data word from the receive FIFO is clocked out onto the RXD[31:0] outputs after each rising edge of the SCLK input. After the entire packet has been clocked out, no more data is clocked out on RXD[31:0] until RXENn is deasserted and reasserted, which allows extra dribble SCLK clock cycles to occur after the end of the packet. RXD[31:0] output data is a 32-bit wide packet data whose format and relationship to the MAC packet and 10-bit PHY data is described in Figure 2.3.

The RXBE[3:0] signals determine which bytes of the 32-bit RXD[31:0] data word contain valid data. RXBE[3:0] are clocked out on the rising edge of SCLK along with each RXD[31:0] data word. Note that RXBE[3:0] = 0b1111 for all words of the packet except the last word, which may end on any one of the 4-byte boundaries of the 32-bit data word. The correspondence between the byte enable inputs and the valid data bytes of each data word on RXD[31:0] is defined in Table 2.2.

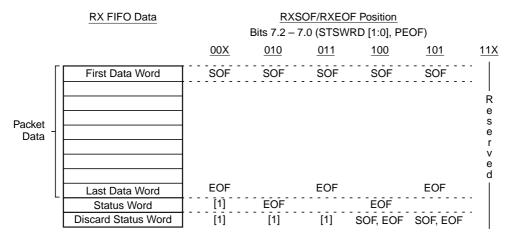

The RXSOF and RXEOF signals indicate which words start and end the Ethernet data packet, respectively. These signals are generally clocked out on the same SCLK rising edge as the first and last word of the data packet, respectively. However, their exact position relative to the data packet is dependent on the programming of the PEOF bit and STSWRD[1:0] bits in Register 7, "Configuration 1". The exact RXSOF and RXEOF position for combinations of these two bits is shown in Figure 2.5. More details about the definition of these bits can be found in "Register 7–Configuration 1," Section 4.3.8, and more details about the status word can be found in Section 2.14, "Receive Status Word,".

2-12

#### Figure 2.5 RXSOF/RXEOF Position

#### Note:

[1] Status words do not exist with this bit combination

The RXWM1 and RXWM2 signals indicate when the receive FIFO has exceeded the programmable watermark thresholds. The watermarks are asserted or deasserted on the rising edge of SCLK, depending on the fullness of the receive FIFO. Refer to Section 2.10, "Receive FIFO," for more details on these watermarks.

RXDC is asserted every time a received packet being output over the system interface is halted and the packet discarded due to some error. This signal is latched HIGH and can be cleared by either asserting the clearing signal, CLR\_RXDC, or cleared automatically if the controller is placed in the AutoClear mode. See Section 2.13, "Packet Discard," section for more details on discards and RXDC.

The RXABORT input, when asserted, discards the current packet being output on the system interface. When RXABORT is asserted, a packet is discarded and the remaining contents of that packet in the receive FIFO are flushed. The process of flushing a receive packet from the receive FIFO with the RXABORT pin requires extra SCLK cycles equal to (packet length in bytes)/8 + 6. Refer to Section 2.13, "Packet Discard," for more information about discarded packets. Clearing the discard RXABORT enable bit in "Register 8–Configuration 2," Section 4.3.9, programs the controller to ignore the RXABORT signal. Setting the

RXABORT definition bit in "Register 9–Configuration 3," Section 4.3.10, also programs the controller to discard either the data packet and its status word or just the data packet exclusive of the status word.

The RXOEn signal, when asserted, places certain receive outputs in the high-impedance state. RXOEn affects the RXD[31:0], RXBE[3:0], RXSOF, and RXEOF output pins.

#### 2.6.4 Bus Width

Setting the BUSSIZE bit in "Register 10–Configuration 4," Section 4.3.11, changes the receive word width from 32-bits to 16-bits. When the bus width is configured to 16-bits, the receive system interface data outputs appear on RXD[15:0] and the data words are now 16-bits wide instead of 32-bits wide.

<u>Note:</u> The transmit word width can be adjusted by appropriately setting the transmit byte enable inputs, TXBE[3:0], as described in Table 2.2.

#### 2.6.5 System Interface Disable

To disable the system interface, set the SINTF\_DIS bit in "Register 9– Configuration 3," Section 4.3.10. When the system interface is disabled, the controller:

- Places all system interface outputs in the high-impedance state (TXWMn[1:2], TXDC, RXD[31:0], RXBE[3:0], RXSOF, RXEOF, RXWM1/2, RXDC)

- Ignores all inputs (SCLK, TXENn, TXD[31:0], TXBE[3:0], TXSOF, TXEOF, CLR\_TXDC, FCNTRL, TXCRCn, RXENn, RXOEn, CLR\_RXDC, RXABORT)

- Transmits /C/ (see Table 2.8) ordered sets with the remote fault bits RF[1:0] = 0b10 over the 10-bit PHY interface outputs

# 2.7 Transmit MAC

To generate an Ethernet MAC frame from the transmit FIFO, the transmit MAC section:

- Generates preamble and SFD

- Pads undersize packets with zeros to meet minimum packet size requirements

- Calculates and appends a CRC value to the packet

- Maintains a minimum interpacket gap

Each of the above four operations can be individually disabled and altered if desired. The transmit MAC then sends the fully formed Ethernet packet to the 8B10B PCS block for encoding. The transmit MAC section also generates MAC control frames.

#### 2.7.1 Preamble and SFD Generation

The transmit MAC normally appends the preamble and SFD to the packet. To program the controller to not append the preamble and SFD to the transmit packet, clear the TXPRMBL bit in "Register 7–Configuration 1," Section 4.3.8.

#### 2.7.2 AutoPad

The transmit MAC normally AutoPads packets. AutoPadding is the process of automatically adding enough zeroes in packets with data fields less than 46 bytes to make the data field exactly 46 bytes in length which meets the 46-byte minimum data field requirement of IEEE 802.3. To program the controller to not AutoPad, clear the APAD bit in "Register 7–Configuration 1," Section 4.3.8.

#### 2.7.3 CRC Generation

The transmit MAC normally appends the CRC value to the packet. To program the controller to not append the CRC value to the end of the packet from the transmit FIFO, assert the TXCRCn pin or clear the TXCRC bit in Register 7 "Configuration 1," as described in Table 2.3 and as described in "Register 7–Configuration 1," Section 4.3.8.

| TXCRC Bit <sup>1</sup> | TXCRCn <sup>2</sup> Pin | CRC Appended to End of Packet? |  |

|------------------------|-------------------------|--------------------------------|--|

| 1                      | 1                       | Yes                            |  |

| 1                      | 0                       | Yes                            |  |

| 0                      | 1                       | No                             |  |

| 0                      | 0                       | Yes                            |  |

Table 2.3 TXRC Bit and TXCRCn Pin Logic

1. 1 = Append, 0 = No append

2. 1 = No append, 0 = Append

#### 2.7.4 Interpacket Gap

If packets from the transmit FIFO arrive at the transmit MAC sooner than the minimum IPG time the transmit MAC adds enough time between packets to equal the minimum IPG value. The default IPG time is set to 96 bits (1 bit = 1 ns).To program other values, set the transmit IPG select bits IPG[2:0] in "Register 7–Configuration 1," Section 4.3.8, as summarized in Table 2.4.

| IPG[2:0]<br>Bits | IPG Value<br>(ns) | Comments                              |  |

|------------------|-------------------|---------------------------------------|--|

| 111              | 96                | IEEE minimum specification            |  |

| 110              | 112               |                                       |  |

| 101              | 80                |                                       |  |

| 100              | 64                |                                       |  |

| 011              | 192               | 2 × IEEE minimum specification        |  |

| 010              | 384               | 4 × IEEE minimum specification        |  |

| 001              | 768               | $8 \times IEEE$ minimum specification |  |

| 000              | 32                |                                       |  |

Table 2.4 Transmit IPG Selection

#### 2.7.5 MAC Control Frame Generation

The transmit MAC can automatically generate and transmit MAC control pause frames, which are used for flow control. This function is described in more detail in Section 2.17, "MAC Control Frames".

# 2.8 Receive MAC

The receive MAC section performs the following operations to disassemble Ethernet packets received from the receive 8B10B PCS section:

- Strips off the preamble and SFD

- Strips off the CRC

- Checks the destination address against the address filters to determine packet validity

- Checks frame validity against the discard conditions

- Checks the length/type field for MAC control frames

Each of the above operations can be individually disabled and altered, if desired. The receive MAC then sends valid packets to the receive FIFO for storage.

#### 2.8.1 Preamble and SFD Stripping

The transmit MAC normally strips the preamble and SFD from the receive packet. To program the controller to not strip the preamble and SFD set the RXPRMBL bit in "Register 7–Configuration 1," Section 4.3.8. When this bit is set, the preamble and SFD are left in the receive packet and are stored in the receive FIFO as a part of the packet.

#### 2.8.2 CRC Stripping

The receive MAC normally strips the FCS from the receive packet. To program the controller to not strip the FCS field, set the RXCRC bit in "Register 7–Configuration 1," Section 4.3.8. When this bit is set the last four bytes of the packet containing the CRC value are left in the receive packet and are stored in the receive FIFO as part of the packet.

#### 2.8.3 Unicast Address Filter

Comparing the destination address of the receive packet against the 48-bit value stored in the three MAC Address registers (registers 0, 1 and 2) filters unicast packets. When the destination address of a unicast packet matches the value stored in these registers the unicast packet is deemed valid and passed to the receive FIFO; otherwise, the packet is rejected. The correspondence between the bits in the MAC Address registers and the incoming bits in the destination address of the receive packet is defined in the MAC Address register definitions.

To program the controller to always reject unicast packets, set the REJUCST bit in "Register 8–Configuration 2," Section 4.3.9. When this bit is set all unicast packets are rejected regardless of their address.

Unicast packet address filtering functions do not affect the reception of MAC control frames. Other bits described in Section 2.17, "MAC Control Frames," control the reception of MAC control frames.

#### 2.8.4 Multicast Address Filter

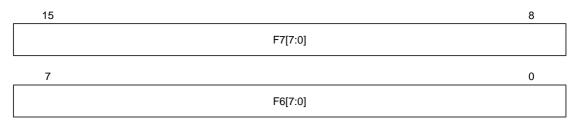

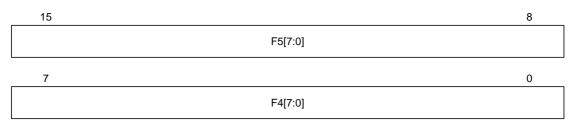

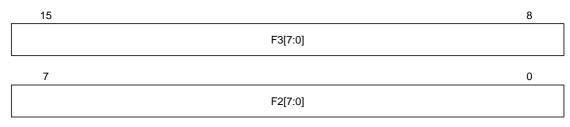

The multicast address filter function computes the CRC on the incoming Destination Address and produces a 6-bit number that is compared against the 64 values stored in the MAC Address Filter 1–4 registers (Registers 3, 4, 5, and 6). When the multicast packet destination address passes the address filter, the packet is deemed valid and passed to the receive FIFO; otherwise, the packet is rejected.

The multicast address filter requires 64 address filter bits to be written into the Address Filter 1–4 registers. The multicast address filtering algorithm is as follows:

- 1. Compute a separate 32-bit CRC on the destination address field using the same IEEE 802.3 defined method that computes the transmit CRC.

- 2. Use bits [0:2] of the destination address FCS to select one of the bytes in the 64-bit address filter, as shown in Table 2.5.

- 3. Use bits [3:5] of the destination address FCS to select one of the bits within the byte selected in (2), as shown in Table 2.5.

- 4. If the bit selected in (3) is a "one" the destination address passes the filter; otherwise, the address fails the filter and the packet is rejected and discarded.

- <u>Note:</u> If all 64 bits of the address filter are programmed to all ones, the address filter passes all multicast addresses.

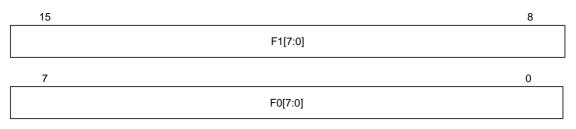

| FCS Bits<br>[0:2] <sup>1</sup> | Address<br>Filter Byte <sup>2</sup> | FCS Bits<br>[3:5] <sup>1</sup> | Address<br>Filter Bit <sup>3</sup> |

|--------------------------------|-------------------------------------|--------------------------------|------------------------------------|

| 000                            | F0[7:0]                             | 000                            | Fx[0]                              |

| 001                            | F1[7:0]                             | 001                            | Fx[1]                              |

| 010                            | F2[7:0]                             | 010                            | Fx[2]                              |

| 011                            | F3[7:0]                             | 011                            | Fx[3]                              |

| 100                            | F4[7:0]                             | 100                            | Fx[4]                              |

| 101                            | F5[7:0]                             | 101                            | Fx[5]                              |

| 110                            | F6[7:0]                             | 110                            | Fx[6]                              |

| 111                            | F7[7:0]                             | 111                            | Fx[7]                              |

#### Table 2.5 Multicast Address Filter Map

1. Bits 0-5 are the six least-significant bits of the CRC.

2. F[7:0] are bytes in Address Filter 1-4 Registers.

3. Fx[7:0] are bits within each byte in Address Filter 1-4 Registers.

Setting the REJMCST bit in "Register 8–Configuration 2," Section 4.3.9, programs the controller to reject all multicast packets regardless of their address. When this bit is set all multicast packets are rejected regardless of their address.

Multicast packet address filtering functions do not affect the reception of MAC control frames. Other bits described in Section 2.17, "MAC Control Frames," control the reception of MAC control frames.

#### 2.8.5 Broadcast Address Filter

The controller does not do any filtering on broadcast packets. To program the controller to reject all broadcast packets, set the REJBCST bit in "Register 8–Configuration 2," Section 4.3.9. When this bit is set all broadcast packets are rejected regardless of their address.

Broadcast address filtering functions do not affect the reception of MAC control frames. Other bits described in Section 2.17, "MAC Control Frames," control the reception of MAC control frames.

#### 2.8.6 Reject or Accept All Packets

Setting the ACPTAL or REJALL bits in "Register 8–Configuration 2," Section 4.3.9, programs the controller to accept or reject all packets regardless of type or whether the packet passes the address filter.

These bits do not affect the reception of MAC control frames. Other bits described in Section 2.17, "MAC Control Frames," control the reception of MAC control frames.

#### 2.8.7 Frame Validity Checks

The receive MAC checks the following to determine the validity of each receive packet:

- Valid FCS

- Oversize packet

- Undersize packet

Computing the CRC value on the incoming receive packet according to IEEE 802.3 specifications and comparing it against the actual CRC value in the FCS field of the received packet determines the validity of the FCS. If the values are not the same, the frame is determined to be invalid and the packet is discarded. Refer to Section 2.13, "Packet Discard" for more information about discards. Clearing the DIS\_CRC error bit in "Register 8–Configuration 2," Section 4.3.9, programs the controller not to discard a packet with a bad FCS.

Oversize packets are packets whose length is greater than the maximum packet size. If a received packet is an oversize packet, then the packet is determined to be invalid and is discarded. Refer to Section 2.13, "Packet Discard" for more information about discards. Clearing the DIS\_OSIZE bit in "Register 8–Configuration 2," Section 4.3.9, programs the controller not to discard an oversize packet and allow packets of unlimited length.

Undersize packets are packets whose length is less than the minimum packet size. Minimum packet size is defined to be 64 bytes, exclusive of preamble and SFD. If a received packet is an undersize packet, the frame is determined to be invalid and is discarded. Refer to Section 2.13, "Packet Discard" for more information about discards. Clearing the DIS\_USIZE bit in "Register 8–Configuration 2," Section 4.3.9, programs the controller not to discard an undersize packet.

## 2.8.8 Maximum Packet Size

The maximum packet size used for receive MAC frame validity checking is programmed to be one of four values, 1518, 1522, 1535 or unlimited bytes. Setting the RMXPKT[1:0] receive MAC maximum packet size select bits in "Register 9–Configuration 3," Section 4.3.10, and the DIS\_OSIZE bit in "Register 8–Configuration 2," Section 4.3.9, as shown in Table 2.6. programs the controller to discard packets that exceed the maximum packet size selected. This selection is also described in the register descriptions for those registers.

The bits shown in Table 2.6 affect the receive MAC section only; the maximum packet size for the management counters is described in Section 2.19, "Counters".

| Register 8<br>DIS_OSIZE Bit | Register 9<br>RMXPKT [1:0] Bits | Maximum<br>Packet Size (Bytes) |

|-----------------------------|---------------------------------|--------------------------------|

| 0b0                         | xx <sup>1</sup>                 | unlimited                      |

| 0b1                         | 0b10                            | 1535                           |

| 0b1                         | 0b01                            | 1522                           |

| 0b1                         | 0b00                            | 1518                           |

Table 2.6

Receive Maximum Packet Size Selection

1. xx = Don't Care

## 2.8.9 MAC Control Frame Check

The length/type field is checked to detect whether the packet is a valid MAC control frame. Refer to Section 2.17, "MAC Control Frames" for more details on MAC control frames.

# 2.9 Transmit FIFO

The transmit FIFO acts as a temporary buffer between the system interface and transmit MAC section. The transmit FIFO size is 4 Kbytes. Data is clocked into the transmit FIFO with the 33–66 MHz system interface clock, SCLK. Data is automatically clocked out of the transmit FIFO with the 125 MHz 8B10B PCS clock whenever a full packet has been loaded into the FIFO (an EOF is written into the FIFO on the system interface), or the FIFO data exceeds the transmit FIFO AutoSend threshold. There are two programmable watermark outputs, TXWM1n and TXWM2n, which aid in managing the data flow into the transmit FIFO.

## 2.9.1 AutoSend

The AutoSend feature causes a packet in the transmit FIFO to be automatically transmitted when data in the transmit FIFO exceeds a certain threshold.

The transmit AutoSend threshold is programmable over the lower 2 Kbytes of the transmit FIFO. The AutoSend threshold can be programmed with the six TASND[5:0] bits that reside in the Transmit FIFO Threshold register. Whenever the data in the FIFO exceeds this threshold, the packet is automatically transmitted to the 8B10B PCS section and out the 10-bit PHY interface. A packet is also automatically transmitted if an EOF is written into the transmit FIFO for that packet, regardless of the AutoSend threshold setting.

All of the bit settings for the transmit AutoSend threshold are evenly distributed over the lower half of the transmit FIFO range, except for the 0b000000 setting. The 0b000000 setting automatically starts transmission when the transmit FIFO is full, thus facilitating the transmission of oversize packets. Refer to "Register 17–Transmit FIFO Threshold," Section 4.3.14, description for more details on the AutoSend (TASND[5:0]) bit settings.

#### 2.9.2 Watermarks

There are two transmit watermarks for the transmit FIFO which are output on the TXWM1n and TXWM2n pins. These watermarks are asserted when the transmit FIFO data exceeds the thresholds associated with the watermarks. The transmit watermark thresholds for TXWM1n and TXWM2n can be programmed over the entire 4 Kbyte FIFO range. Each of the watermark thresholds is independently programmed with five bits that reside in the Transmit FIFO Threshold register. Whenever the data in the FIFO exceeds the threshold of either watermark, the respective watermark pin on TXWM1n or TXWM2n is asserted LOW. The watermark signals stay asserted until the data in the FIFO goes below the respective thresholds.

#### 2.9.3 TX Underflow

The transmit FIFO underflow condition occurs when the TX FIFO is empty but the MAC is still requesting data to complete the transmission of a packet. If the transmit FIFO underflows:

- Packet transmission to the 8B10B PCS is halted

- A /V/ code (see Table 2.8) is appended to the end of the partially transmitted packet

- Any new data for the partially transmitted packet is discarded

Refer to Section 2.13, "Packet Discard" for more information about discards.

#### 2.9.4 TX Overflow

The transmit FIFO overflow condition occurs when the TX FIFO is full but additional data is still being written into it from the system interface. If the transmit FIFO overflows:

- The input to the TX FIFO is blocked and does not accept any more data from the system interface until the TX FIFO space is freed up

- The data already stored in the TX FIFO for the partially loaded last packet is transmitted with a /V/ code (see Table 2.8) appended to the end of the packet to indicate an error

- Any new data for the partially loaded last packet is discarded

Refer to Section 2.13, "Packet Discard" for more information about discards.

## 2.9.5 Link Down FIFO Flush

When the link is down (also referred to as link fail) and defined by either receiver has lost sync or AutoNegotiation process has not yet completed, the transmitter at the 10-bit PHY interface is occupied with sending either idle or AutoNegotiation codes (/I/ or /C/ see Table 2.8). As a result, data cannot exit the transmit FIFO to the transmit MAC section. If data continues to be input to the transmit FIFO from the system interface while the controller is in the link fail mode the transmit FIFO may overflow. Enabling the link down FIFO flush feature causes the data exiting the transmit FIFO to be automatically discarded when the controller is in the link fail mode, thus preventing any possible overflow of the transmit FIFO. Setting the Link Down FIFO Flush Enable bit (LNKDN) in "Register 10–Configuration 4," Section 4.3.11, enables the link down FIFO flush mode.

# 2.10 Receive FIFO

The receive FIFO acts as a temporary buffer between the receive MAC section and system interface. The receive FIFO size is 16 Kbytes. Data is clocked into the receive FIFO with the 125 MHz 8B10B PCS clock. Data is clocked out of the receive FIFO with the 33–66 MHz system interface clock, SCLK. There are two programmable watermark outputs, RXWM1 and RXWM2, which aid in managing the data flow out of the receive FIFO.

#### 2.10.1 Watermarks

There are two watermarks for the receive FIFO. which are output on the RXWM1 and RXWM2 pins. These watermarks are asserted when the receive FIFO data exceeds the thresholds associated with the watermarks.

The receive watermark thresholds for RXWM1 and RXWM2 can be programmed over the entire 16 Kbyte receive FIFO range. Each of the watermark thresholds is independently programmed with eight bits that reside in the Receive FIFO Threshold register. Whenever the data in the FIFO exceeds the threshold of either watermark, the respective watermark pin on either RXWM1 or RXWM2 is asserted HIGH. RXWM2 is also asserted if a complete packet is loaded into the receive FIFO from the 8B10B PCS section. The watermarks stay asserted until the data in the FIFO goes below the respective thresholds, and RXWM2 also stays asserted until all end of packets (EOF) have been read out of the receive FIFO. After the EOFs have been read out of the receive FIFO, the watermarks cannot go active again until RXENn is deasserted.

#### 2.10.2 RX Overflow

The receive FIFO overflow condition occurs when the receive RX FIFO is full and additional data is still being written into it from the MAC. If the receive FIFO overflows:

- The input to the RX FIFO is blocked and does not accept any more data from the 8B10B PCS until RX FIFO space is freed up

- The data already stored in the RX FIFO for the partially loaded last packet is normally discarded

- Any new data for the partially loaded last packet is also normally discarded

Refer to Section 2.13, "Packet Discard" for more information about discards. Clearing the DIS\_OVF bit in "Register 8–Configuration 2," Section 4.3.9, programs the controller to not discard a packet corrupted by overflow.

## 2.10.3 RX Underflow

The receive FIFO underflow condition occurs when the system interface is attempting to read data out of the RX FIFO when it is empty. If the RX FIFO underflows, any data read out of the RX FIFO while the underflow condition persists is invalid, and any new data for the partially loaded last packet is stored in the RX FIFO and is not discarded.

# 2.11 8B10B PCS

The 8B10B PCS has a transmit section and a receive section.

The transmit 8B10B PCS section accepts Ethernet formatted packet data from the transmit MAC and:

- Encodes the data with the 8B10B encoder

- Adds the start of packet delimiter

- Adds the end of packet delimiter

- Adds the idle code stream

- Formats the packet according to the 10B PHY format defined in IEEE 802.3z and shown in Figure 2.3

The 8B10B encoded data stream is then sent to the transmit 10-bit PHY interface for transmission.

The transmit 8B10B PCS section also generates the AutoNegotiation code stream when the controller is in the AutoNegotiation process.

The receive 8B10B PCS section takes the 8B10B encoded packet data from the incoming 10-bit PHY interface and:

- Acquires and maintains word synchronization

- Strips off the start of packet delimiter

- Strips off the end of packet delimiter

- Strips off the idle code stream

- Decodes the data with the 8B10B decoder

- Converts the packet to the Ethernet packet format shown in Figure 2.2

The Ethernet packet is then sent to the receive MAC for processing.

The receive 8B10B PCS section also decodes the AutoNegotiation code stream when the controller is in the AutoNegotiation process.

#### 2.11.1 8B10B Encoder

The 8B10B encoder converts each data byte of a packet into a unique 10-bit word as defined in IEEE 802.3z and shown in Table 2.7 (in abbreviated form).

| 8B Bytes          |                  | 108                       | 3 Codes                   |

|-------------------|------------------|---------------------------|---------------------------|

| Data Byte<br>Name | Bits<br>HGFEDCBA | CurrentRD–<br>abcdei fghj | CurrentRD+<br>abcdei fghj |

| D0.0              | 000 00000        | 100111 0100               | 011000 1011               |

| D1.0              | 000 00001        | 011101 0100               | 100010 1011               |

| D2.0              | 000 00010        | 101101 0100               | 010010 1011               |

| D3.0              | 000 00011        | 110001 1011               | 110001 0100               |

| •<br>•            | •<br>•           |                           | ·<br>·                    |

| D28.7             | 111 11100        | 001110 1110               | 001110 0001               |

| D29.7             | 111 11101        | 101110 0001               | 010001 1110               |

| D30.7             | 111 11110        | 011110 0001               | 100001 1110               |

| D31.7             | 111 11111        | 101011 0001               | 010100 1110               |

| Table 2.7 | 8B10B | Coding | Table |

|-----------|-------|--------|-------|

|-----------|-------|--------|-------|

The encoder also converts the start of packet delimiter, end of packet delimiter, idle code streams, and AutoNegotiation code streams into unique 10B code words. These unique 10B code words are referred to as ordered sets. Table 2.8 describes the ordered sets defined and used by IEEE 802.3z.

The 8B10B encoder also keeps the running disparity of the outgoing 10B word as close as possible to zero. Running disparity is the difference between the number of ones and zeros transmitted on the outgoing bit stream. The algorithm for calculating running disparity is defined in 802.3z. After each 10B word is transmitted, the running disparity is recalculated. If the current running disparity is negative, the next 10B word is chosen from the "Current RD–" column in Table 2.7 (in abbreviated form). If the current running disparity is positive, the next 10B word is chosen from the "Current RD+" column in Table 2.7.

## 2.11.2 8B10B Decoder

The 8B10B decoder performs the reverse process of the 8B10B encoder. The 8B10B decoder converts each 10-bit word back into an 8-bit byte using the code conversion tables defined in IEEE 802.3z and shown in Table 2.7 (in abbreviated form) and Table 2.8. The 8B10B decoder also checks the running disparity of the incoming 10B word to insure that it is correct.

A PCS codeword error results if the 8B10B decoder detects any of the following:

- A 10B word that is not valid (does not appear in Table 2.7)

- An ordered set that is not valid (does not appear in Table 2.8)

- An error in the running disparity

Packets with PCS codeword errors are normally discarded. Refer to Section 2.13, "Packet Discard" for more details on discards. Clearing the DIS\_CWRD bit in "Register 8–Configuration 2," Section 4.3.9, programs the controller to not discard a packet with PCS codeword errors.

| 10B Code<br>Symbol | Description             | 10B Codes                                                       | Begin<br>RD | End<br>RD         |

|--------------------|-------------------------|-----------------------------------------------------------------|-------------|-------------------|

| /C1/               | Link<br>Configuration 1 | /K28.5/ <sup>1</sup><br>/D21.5/<br>config_word1<br>config_word2 | + or -      | flip <sup>2</sup> |

| /C2/               | Link<br>Configuration 2 | /K28.5/ <sup>1</sup><br>/D2.2/<br>config_word1<br>config_word2  | + or –      | same <sup>2</sup> |

| /C/                | Link<br>Configuration   | Alternating<br>/C1/ & /C2/                                      | -           | -                 |